NAND gate S-R flip-flop

PARTS AND MATERIALS

- 4011 quad NAND gate (Radio Shack catalog # 276-2411)

- 4001 quad NOR gate (Radio Shack catalog # 276-2401)

- Eight-position DIP switch (Radio Shack catalog # 275-1301)

- Ten-segment bargraph LED (Radio Shack catalog # 276-081)

- One 6 volt battery

- Three 10 kΩ resistors

- Two 470 Ω resistors

Caution! The 4011 IC is CMOS, and therefore sensitive to static electricity!

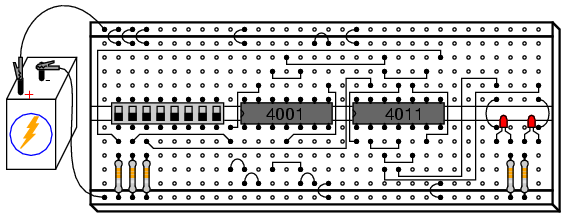

Although the parts list calls for a ten-segment LED unit, the illustration shows two individual LEDs being used instead. This is due to lack of room on my breadboard to mount the switch assembly, two integrated circuits, and the bargraph. If you have room on your breadboard, feel free to use the bargraph as called for in the parts list, and as shown in prior latch circuits.

CROSS-REFERENCES

Lessons In Electric Circuits, Volume 4, chapter 3: "Logic Gates"

Lessons In Electric Circuits, Volume 4, chapter 10: "Multivibrators"

LEARNING OBJECTIVES

- The difference between a gated latch and a flip-flop

- How to build a "pulse detector" circuit

- Learn the effects of switch contact "bounce" on digital circuits

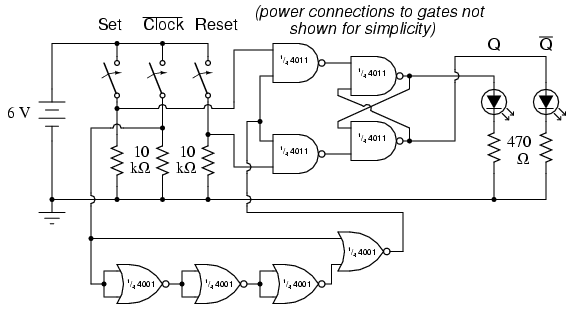

SCHEMATIC DIAGRAM

ILLUSTRATION

INSTRUCTIONS

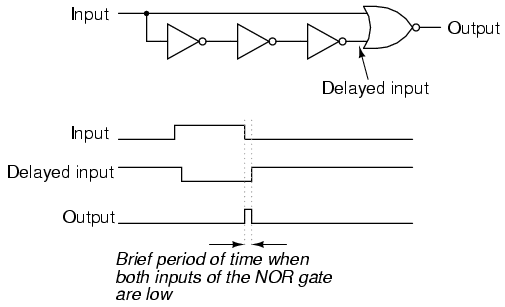

The only difference between a gated (or enabled) latch and a flip-flop is that a flip-flop is enabled only on the rising or falling edge of a "clock" signal, rather than for the entire duration of a "high" enable signal. Converting an enabled latch into a flip-flop simply requires that a "pulse detector" circuit be added to the Enable input, so that the edge of a clock pulse generates a brief "high" Enable pulse:

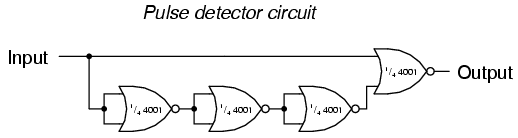

The single NOR gate and three inverter gates create this effect by exploiting the propagation delay time of multiple, cascaded gates. In this experiment, I use three NOR gates with paralleled inputs to create three inverters, thus using all four NOR gates of a 4001 integrated circuit:

Normally, when using a NOR gate as an inverter, one input would be grounded while the other acts as the inverter input, to minimize input capacitance and increase speed. Here, however, slow response is desired, and so I parallel the NOR inputs to make inverters rather than use the more conventional method.

Please note that this particular pulse detector circuit produces a "high" output pulse at every falling edge of the clock (input) signal. This means that the flip-flop circuit should be responsive to the Set and Reset input states only when the middle switch is moved from "on" to "off," not from "off" to "on."

When you build this circuit, though, you may discover that the outputs respond to Set and Reset input signals during both transitions of the Clock input, not just when it is switched from a "high" state to a "low" state. The reason for this is contact bounce: the effect of a mechanical switch rapidly making-and-breaking when its contacts are first closed, due to the elastic collision of the metal contact pads. Instead of the Clock switch producing a single, clean low-to-high signal transition when closed, there will most likely be several low-high-low "cycles" as the contact pads "bounce" upon off-to-on actuation. The first high-to-low transition caused by bouncing will trigger the pulse detector circuit, enabling the S-R latch for that moment in time, making it responsive to the Set and Reset inputs.

Ideally, of course, switches are perfect and bounce-free. In the real world, though, contact bounce is a very common problem for digital gate circuits operated by switch inputs, and must be understood well if it is to be overcome.